# Fabrication of Transferable Al<sub>2</sub>O<sub>3</sub> Nanosheet by Atomic Layer Deposition for Graphene FET

Hanearl Jung,<sup>||,‡</sup> Jusang Park,<sup>||,‡</sup> Il-Kwon Oh,<sup>‡</sup> Taejin Choi,<sup>‡</sup> Sanggeun Lee,<sup>§</sup> Juree Hong,<sup>§</sup> Taeyoon Lee,<sup>§</sup> Soo-Hyun Kim,<sup> $\perp$ </sup> and Hyungjun Kim<sup>\*,‡</sup>

<sup>‡</sup>Nanodevice Laboratory, School of Electrical and Electronic Engineering, and <sup>§</sup>Nanobio Device Laboratory, School of Electrical and Electronic Engineering, Yonsei University, Seodaemun-Gu, Seoul 120-749, Republic of Korea

<sup>1</sup>School of Materials Science and Engineering, Yeungnam University, 214-1, Dae-dong, Gyeongsan-Si 712-749, Republic of Korea

## Supporting Information

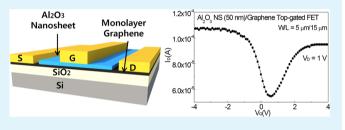

**ABSTRACT:** Without introducing defects in the monolayer of carbon lattice, the deposition of high- $\kappa$  dielectric material is a significant challenge because of the difficulty of high-quality oxide nucleation on graphene. Previous investigations of the deposition of high- $\kappa$  dielectrics on graphene have often reported significant degradation of the electrical properties of graphene. In this study, we report a new way to integrate high- $\kappa$  dielectric nanosheet onto graphene. Al<sub>2</sub>O<sub>3</sub> film was deposited on a

sacrificial layer using an atomic layer deposition process and the  $Al_2O_3$  nanosheet was fabricated by removing the sacrificial layer. Top-gated graphene field-effect transistors were fabricated and characterized using the  $Al_2O_3$  nanosheet as a gate dielectric. The top-gated graphene was demonstrated to have a field-effect mobility up to 2200 cm<sup>2</sup>/(V s). This method provides a new method for high-performance graphene devices with broad potential impacts reaching from high-frequency high-speed circuits to flexible electronics.

KEYWORDS: graphene, gate dielectric, atomic layer deposition, Al<sub>2</sub>O<sub>3</sub>, nanosheet, top-gated field effect transistor

# INTRODUCTION

Since the discovery of graphene in 2004,<sup>1</sup> this single-layer, thin, hexagonal carbon atom structure (one carbon atom thickness is approximately 0.34 nm) with very high mobility (greater than 200,000  $\text{cm}^2/(\text{V s})$  at 4.2 K for suspended<sup>2</sup>) has drawn attention as a promising material for future nanoelectronics and as a substitute for silicon. In recent years, considerable research has been performed to grow large-area graphene. Wafer-scale graphene has been synthesized<sup>3</sup> and continuous roll-to-roll growth of graphene has been reported.<sup>4</sup> Graphene-based electronic devices may be fabricated using technologies similar to conventional silicon-based electronic devices. To apply conventional technologies to graphene, various studies have been performed; however, some of them could not be directly used to fabricate graphene-based devices. For example, graphene is seriously damaged by the sputtering process, and so it cannot be directly applied to graphene fabrication.<sup>5</sup>

For conventional nanoelectronic devices, atomic layer deposition (ALD) is an appropriate deposition technique for controlled thickness and ultrathin homogeneous films. However, ALD of thin films on graphene is not easy because there are only sp2 bonds and no dangling bonds on the defect-free graphene surface, which are needed for chemical surface reactions. Experimental observation of ALD on graphene also has been performed.<sup>6</sup> Nevertheless, some researchers have been able to deposit thin films, such as  $HfO_2^{7,8}$  and  $Al_2O_3^{9,10}$  on

pristine graphene and fabricate top-gated devices with good performance. To deposit smooth, uniform films on graphene, the surface has to be pretreated to produce more dangling bonds, which act as nucleation sites. NO<sub>2</sub> functionalization<sup>11</sup> and ozone treatment<sup>12</sup> have been successfully used in the deposition of thin films on carbon nanotubes;<sup>13,14</sup> other approaches for pretreated graphene have also been applied. For example, a thin ( $\sim$ 1 nm thick) seed layer of evaporated metal was oxidized before ALD<sup>15</sup> or polymer films were used as a buffer layer for ALD.<sup>6</sup> Recently, there have been reports of physically transferred dielectric materials for graphene devices. Duan et al. reported a transfer process of Al<sub>2</sub>O<sub>3</sub> nanoribbons using contact printing on exfoliated graphene<sup>16</sup> or top-gateelectrode/dielectric-layer-stacks on chemical vapor deposition (CVD)-grown graphene<sup>17</sup> to produce top-gated graphene field effect transistor (FET). Lee et al. fabricated a physically transferrable Al2O3 layer using Cu foil and used it as gate insulator layer of a graphene-carbon nanotube FET.<sup>18</sup> Theses researches demonstrate the production of gate oxide layers using physical bonds instead of chemical bonds, which showed good dielectric characteristics. So they opened a new way for

Received:November 22, 2013Accepted:February 3, 2014Published:February 3, 2014

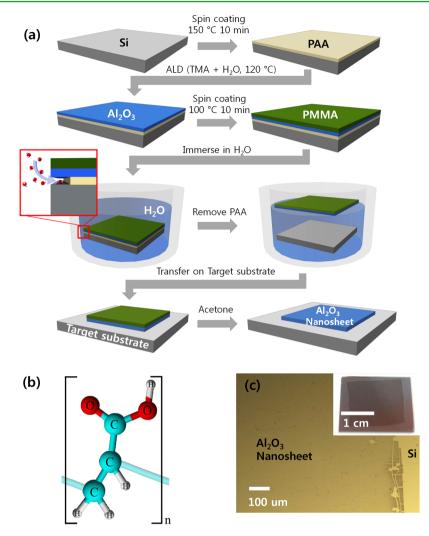

Figure 1. (a) Schematic of the  $Al_2O_3$  nanosheet fabrication process. (b) Chemical structure of poly(acrylic acid). (c) Optical microscope image of the transferred  $Al_2O_3$  nanosheet (30 nm) on the Si substrate (Inset: optical image of the transferred  $Al_2O_3$  nanosheet (30 nm) on a Si substrate).

fabricating devices regardless of materials using conventional equipment.

Here we report the realization of a top-gated graphene FET without any chemical or physical treatments on graphene. A transferrable  $Al_2O_3$  nanosheet (NS) was fabricated using the ALD process and a sacrificial layer. Top-gated graphene FETs using both transferrable  $Al_2O_3$  NS and thermal ALD (Th-ALD)  $Al_2O_3$  on CVD-grown graphene were fabricated for comparison study and their electrical characteristics were investigated.

# EXPERIMENTAL SECTION

Initially, an water-soluble poly(acrylic) acid (PAA) (Alfa Aesar, molecular weight of PAA = 244 000 g/mol) as a sacrificial layer was formed on the Si substrate by spin-coating and annealed at 150 °C for 10 min under ambient conditions to evaporate the solvents of PAA. After annealing,  $Al_2O_3$  thin film was deposited on the sacrificial layer using a homemade thermal ALD (Th-ALD) at 120 °C with trimethyl aluminum (TMA) and  $H_2O$  as precursors of Al and O, respectively. ALD is a kind of CVD process using chemical reaction between hydroxyl groups on the substrates and ligands of the precursor or reactant. However, most of the widely used polymers, such as polyethylene, poly(vinyl chloride) and polystyrene, do not have hydroxyl groups in the chemical structure. So, the mechanisms of ALD on the polymer are adsorption of precursors on the surface or absorption of precursors into the near surface region, which result in nucleation delays of the initial ALD process.<sup>19</sup> Therefore,  $Al_2O_3$  could

be deposited on PAA using the ALD process because of the hydroxyl group of PAA. The sample was then covered with poly(methyl methacrylate) (PMMA) as a supporting layer for reducing tearing problems during the transfer process and annealed at 100 °C for 10 min to enhance the adhesion between PMMA and the Al<sub>2</sub>O<sub>2</sub> thin film. The solubility of PAA in water facilitated the use of PMMA as a polymer-supporting layer. In Figure 1a, step 4, both top-side (PMMA, the supporting layer) and bottom-side (PAA, the sacrificial layer) of the Al<sub>2</sub>O<sub>3</sub> thin film were polymers and both polymers must be removed to obtain Al2O3 NS. Acetone cannot be used because it removes both the sacrificial and supporting layers. Therefore, watersoluble PAA was used as the sacrificial layer because water removes only the sacrificial layer. By dipping the sample in water, the sacrificial layer was removed and the Al<sub>2</sub>O<sub>3</sub> NS floated on the surface of water and it was scooped up by a target substrate. The supporting layer was then removed using acetone, isopropyl alcohol, and deionized water and then dried with nitrogen gas. The thickness of the Al<sub>2</sub>O<sub>3</sub> NS was measured by ellipsometry. The surface morphology and interface between the transferred NS and target substrate were investigated using scanning electron microscopy (SEM) and atomic force microscopy (AFM). The dielectric properties of the transferred  $Al_2O_3\ N\bar{S}$  were investigated by preparing  $Ru/Al_2O_3/p$ -type Si metaloxide silicon (MOS) capacitors.

A monolayer graphene was grown using a conventional CVD method at 1000  $^{\circ}$ C with methane and hydrogen gas. The monolayer graphene was certified using a Raman spectroscopy. Graphene was transferred to a 300 nm silicon oxide and graphene channel was

patterned using photolithography and oxygen plasma treatments. On top of the graphene, 50 nm of  $Al_2O_3$  NS was transferred and 50 nm of Th-ALD  $Al_2O_3$  thin film was deposited as gate insulators. To remove water under the  $Al_2O_3$  NS and to enhance adhesion between NS and graphene for reduce peeling problem (see Figure S3 in the Supporting Information), we annealed samples at 200 °C in the vacuum with hydrogen and argon gases for about 30 min. Then, both  $Al_2O_3$  were patterned and etched using photolithography. Finally, source, drain, and top gate electrode (50 nm Ti) of graphene FET were deposited using the evaporation and a lift-off process. The electrical properties of the MOS capacitors and top-gated graphene FETs were measured using a probe station (Keithley 306 electrometer).

# RESULTS AND DISCUSSION

Figure 1a shows the fabrication process of  $Al_2O_3$  NS using a sacrificial layer and ALD process. The water-soluble PAA, a sacrificial layer in this study, has a hydroxyl group on its chemical structure (Figure 1b) that can act as a nucleation site for the precursor and reactant in the ALD process. Due to the hydroxyl group of PAA,  $Al_2O_3$  thin film was deposited on PAA and  $Al_2O_3$  NS was successfully transferred to the target substrate. An optical microscope image of the transferred  $Al_2O_3$  NS (30 nm) on the Si substrate is shown in Figure 1c. Some cracks and fragments are observed on the edge of the NS (right side of the image); however, the inner part of the NS is quite clean and uniform. A large area and uniform NS is observed in the inset image. The largest size of NS with this process is about 5 cm and minimum thickness is about 7 nm (see Figure S1 in the Supporting Information).

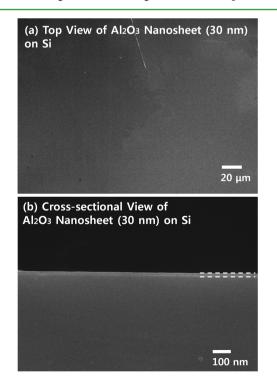

A flat and clean surface of  $Al_2O_3$  NS is observed in the top SEM image (Figure 2a). We especially chose this area for the fine focusing by using a crevice (white line in the image). Overall, the surface has no wrinkles or folded regions. If the surface is not flat and air gaps between the  $Al_2O_3$  NS and graphene are generated during the transfer process, the

Figure 2. (a) Top and (b) cross-sectional SEM image of the transferred  $Al_2O_3$  nanosheet (30 nm) on a Si substrate.

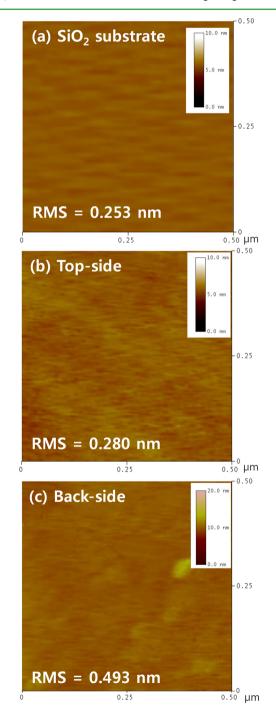

electrical properties of the devices would be degraded. If there are air gaps between  $Al_2O_3$  NS and graphene, the air gaps would connect in series with  $Al_2O_3$  NS and graphene vertically. As a result, series capacitors with very low permittivity of the air ( $\varepsilon_{air} = 1.0006$ ) would be generated and they would degrade the characteristics of the devices by decreasing the gate capacitance.<sup>18</sup> However, no air gaps are observed between  $Al_2O_3$  NS and the substrate in the cross-sectional SEM image (Figure 2b), indicating the transferred NS is quite flat and successfully transferred to the Si substrate. The flat surface of  $Al_2O_3$  NS is also observed in the AFM image. Figure 3a is an

Figure 3. AFM measurements on the (a)  $SiO_2$  substrate, (b) top-side, and (c) back-side of the transferred  $Al_2O_3$  (30 nm) nanosheet on a Si substrate.

AFM image of SiO<sub>2</sub> substrate and it shows very flat with very low root mean square (RMS) roughness about 0.253 nm. Figure 3b is a top-side AFM image of Al<sub>2</sub>O<sub>3</sub> NS. The surface of transferred Al<sub>2</sub>O<sub>3</sub> NS is very flat with low surface roughness follows by flat SiO<sub>2</sub> substrate and its RMS roughness is 0.280 nm. However, from a previous report of ALD on polymers, the interface between the ALD thin film and some of polymers have a mixed structure of oxide and polymer materials due to the mechanisms of ALD on the polymer.<sup>19</sup> To confirm the interface structure, the back-side of the transferred Al<sub>2</sub>O<sub>3</sub> NS is observed using AFM. The back-side of the Al<sub>2</sub>O<sub>3</sub> NS samples are prepared using a process similar to the "pick up" method.<sup>20</sup> Al<sub>2</sub>O<sub>3</sub> NS floating on the water surface is picked up with the Si substrate. The back-side of the Al<sub>2</sub>O<sub>3</sub> NS surface is nearly flat but small dots are observed in Figure 3c. The dots are assumed to be residue of partially melted PAA and these dots have negligible effects on the properties of Al<sub>2</sub>O<sub>3</sub> NS because they are very small and the overall back-side surface is also quite flat.

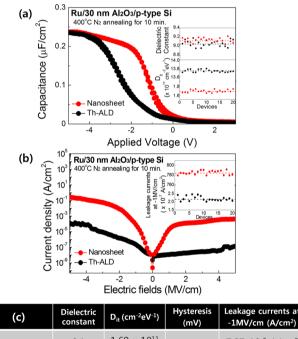

Ru/30 nm Al<sub>2</sub>O<sub>3</sub> NS/p-type Si MOS capacitors are fabricated to investigate the electrical properties of Al<sub>2</sub>O<sub>3</sub> NS. MOS capacitors using Th-ALD Al<sub>2</sub>O<sub>3</sub> on Si are also fabricated for the comparison study. Both samples are annealed at 400 °C in a N<sub>2</sub> condition for 10 minutes. Figure 4 shows the (a)

|           |                |                                    | (   |                                                    |

|-----------|----------------|------------------------------------|-----|----------------------------------------------------|

| Nanosheet | 9.1<br>(± 1 %) | 1.69 x 10 <sup>11</sup><br>(± 6 %) | ~ 0 | 7.87x10 <sup>-5</sup> A/cm <sup>2</sup><br>(± 1 %) |

| Th-ALD    | 9.0<br>(± 1 %) | 1.37 x 10 <sup>12</sup><br>(± 5 %) | ~ 0 | 2.21x10 <sup>-7</sup> A/cm <sup>2</sup><br>(± 7 %) |

|           |                |                                    |     |                                                    |

Figure 4. (a) C-V and (b) I-V measurements of the transferred Al<sub>2</sub>O<sub>3</sub> nanosheet (30 nm) and Th-ALD Al<sub>2</sub>O<sub>3</sub> (30 nm) on the p-type Si substrates (Inset: (a) dielectric constants and interface state densities for 20 devices, (b) leakage currents at -1 MV/cm for 20 devices). (c) Summary of the dielectric properties of 30 nm of Al<sub>2</sub>O<sub>3</sub> nanosheet and Th-ALD Al<sub>2</sub>O<sub>3</sub>.

capacitance–voltage (C-V), (b) current–voltage (I-V) curves and (c) a summary of the dielectric properties of transferred Al<sub>2</sub>O<sub>3</sub> NS and Th-ALD Al<sub>2</sub>O<sub>3</sub>. The calculated dielectric constant of Al<sub>2</sub>O<sub>3</sub> NS is approximately 9.1 and it is nearly the same as that of Th-ALD Al<sub>2</sub>O<sub>3</sub> (dielectric constant 9.0).

The interface state density  $(D_{it})$  value of Al<sub>2</sub>O<sub>3</sub> NS is 1.69 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> and its hysteresis is nearly 0 mV, implying the trap charge density and trapped oxide charges between transferred Al<sub>2</sub>O<sub>3</sub> NS and the Si substrate are nearly zero. Therefore, the interface between the Al<sub>2</sub>O<sub>3</sub> NS and Si substrate is formed to a clean junction. A negative flat band voltage shift is observed for the Th-ALD Al<sub>2</sub>O<sub>3</sub> film, which is caused by positive fixed oxide charges. Some previous studies reported the negative shift of the flat band voltage at low temperature ALD (100-150 °C) of Al<sub>2</sub>O<sub>3</sub> films<sup>21,22</sup> and the Th-ALD Al<sub>2</sub>O<sub>3</sub> film in this study is also deposited at a low temperature of 120 °C. In Figure 4b, the Al<sub>2</sub>O<sub>3</sub> NS shows a slightly larger leakage current than that of Th-ALD Al<sub>2</sub>O<sub>3</sub> but its value is quite small and negligible. Al<sub>2</sub>O<sub>3</sub> NS has more enhanced dielectric properties than Th-ALD Al<sub>2</sub>O<sub>3</sub> film. Al<sub>2</sub>O<sub>3</sub> NS has a 10 times lower D<sub>it</sub> and smaller flat band voltage shift than Th-ALD Al<sub>2</sub>O<sub>3</sub> film. The  $D_{it}$  and flat band voltage shift are affected by interfacetrapped charges and fixed-oxide charges that exist at the interface of the deposited film and substrate, respectively. For  $Al_2O_3$  NS, some opposite charges in the water may be attached to the bottom of NS by columbic attraction during the transfer process, resulting in the suppressing the effects of charges in the films. Finally, they reduce  $D_{it}$  and flat band voltage shift. Calculated dielectric constants, D<sub>it</sub>, and leakage currents for 20 devices are shown in the insets of panels a and b in Figure 4. They imply that Al<sub>2</sub>O<sub>3</sub> NS and Th-ALD Al<sub>2</sub>O<sub>3</sub> films have quite good uniformity.

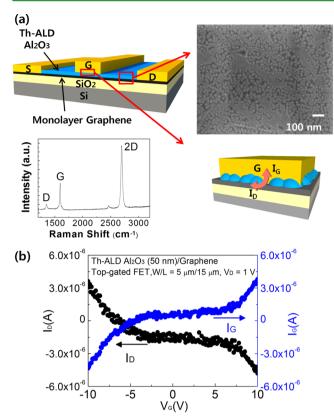

Top-gated graphene FETs are fabricated with Th-ALD Al<sub>2</sub>O<sub>3</sub> directly on graphene for a comparison study of FET using Al<sub>2</sub>O<sub>3</sub> NS. Figure 5a shows a schematic of the top-gated graphene FET using Th-ALD Al<sub>2</sub>O<sub>3</sub> (left above), the gate electrode/Th-ALD Al<sub>2</sub>O<sub>3</sub> /graphene stack (right below) and an SEM image of the Th-ALD Al<sub>2</sub>O<sub>3</sub> /graphene (right above). The left below graph of Figure 5a is the Raman spectroscopy of the CVD grown graphene transferred on the SiO<sub>2</sub> substrate, showing typical features of monolayer graphene; ~0.5 of the Gto-2D intensity ratio, the G band centered at 1593 with a full width at half maximum (FWHM) of 15.1 and the 2D band at 2691 with a FWHM of 33.4.<sup>23,24</sup> The small D peak comes from the transfer process. As shown in the SEM image of Th-ALD 50 nm  $Al_2O_3$ /graphene/SiO<sub>2</sub> (Figure 5a, right above), poor coverage of the  $Al_2O_3$  thin films is observed, which is similar to previous reports of poor wetting of Al<sub>2</sub>O<sub>3</sub> thin films grown by un-seeded ALD on a monolayer graphene/SiO<sub>2</sub> substrate.<sup>2</sup> The SEM image of Th-ALD Al<sub>2</sub>O<sub>3</sub> on the monolayer graphene shows an island-like growth mode resulting in poor wetting of Th-ALD Al<sub>2</sub>O<sub>3</sub> on graphene. Figure 5b) shows the drainsource current  $(I_D)$  and drain-gate current  $(I_G)$  versus gate voltage  $(V_G)$  curves of the fabricated device. Large  $I_G$  comes from primarily uncovered regions of Th-ALD  $Al_2O_3$  on graphene because of the island-like growth mode (Figure 5a right above) and they make direct connections between the gate electrode and the graphene channel (Figure 5a right below) and produce a large  $I_G$  nearly the same as  $I_D$ . Nearly all of the  $I_D$  flows through the gate electrode ( $I_G$ ), indicating the Al<sub>2</sub>O<sub>3</sub> film by direct Th-ALD on graphene did not work as a gate oxide layer.

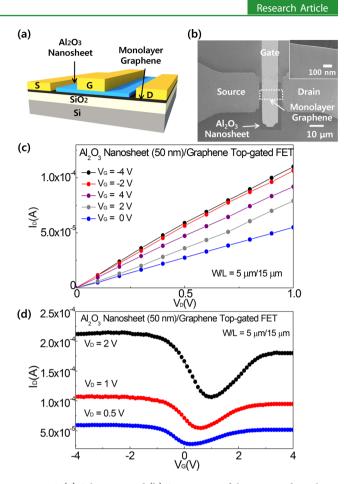

Panels a and b in Figure 6 show a schematic representation of the top-gated graphene FET using  $Al_2O_3$  NS and a SEM image of the fabricated top-gated graphene FET, respectively. The electrical transport studies of the top-gated graphene FETs are performed at room temperature. Figure 6c shows the  $I_D$  versus drain-source voltage ( $V_D$ ) output characteristics of the

Figure 5. (a) Schematic of the top-gated graphene FET using Th-ALD  $Al_2O_3$  (left), the SEM image of Th-ALD  $Al_2O_3$  on the monolayer graphene (right above) and the schematic of the gate-electrode/Th-ALD  $Al_2O_3$ /graphene stack (right below) (Inset: Raman spectrum of monolayer graphene transferred on a 300 nm SiO<sub>2</sub> substrate). (b) Drain-source current ( $I_D$ ) and drain-gate current ( $I_G$ ) versus gate voltage ( $V_G$ ) curves of top-gated graphene FET using Th-ALD  $Al_2O_3$ .

FET at various  $V_{\rm G}$  of -4, -2, 0, 2, and 4 V. The device delivers an on-current of 108  $\mu$ A at  $V_D$  = 1 V and  $V_G$  = -4 V. The transfer characteristics of the top-gated graphene FET are measured from -4 to +4 V gate bias in Figure 6d. As shown in a family of  $I_{\rm D}$  versus  $V_{\rm G}$  curves with different drain bias  $V_{\rm D}$ values (Figure 6d), the increase in  $V_{\rm D}$  induces the increased overall current and shifts in the curves to the positive voltage direction. This drain-induced Dirac voltage shifting is also observed in previous reports,<sup>26–28</sup> as the drain-induced channel potential weakens the gate control. In ambipolar transistors, the Dirac point, the minimum current point, is reached when the injected electron and hole currents from the source-drain are balanced. Therefore, equal and opposite voltages  $(\pm 1/2 V_{\rm D})$  to the source and drain are required to hold the Dirac point at a zero gate voltage. Therefore, the gate-source or gate-drain potential difference, which is also the Dirac voltage when either the source or drain is grounded, will shift by  $1/2\Delta V_{\rm D}$  with a change of  $\Delta V_{\rm D}$ . In our device, the Dirac voltage shifts approximately 0.7 V when  $V_{\rm D}$  increases from 0.5 to 2 V, close to the theoretical prediction.<sup>26,29,30</sup> The field-effect mobility is extracted based on the slope  $(\Delta I_{\rm D})/(\Delta V_{\rm G})$  fitted to the linear regime of the transfer curves using the equation  $\mu$ =  $((\Delta I_D)/(\Delta V_G))(1/(V_D C_{OX})L/W)$  where L and W are the channel length and width, and  $C_{OX}$  is the gate oxide capacitance. The extracted field-effect mobilities for the device are  $\sim 2200 \text{ cm}^2/(\text{V s})$  and  $\sim 800 \text{ cm}^2/(\text{V s})$  for the hole and the electron, respectively. The electron-hole asymmetry is origi-

Figure 6. (a) Schematic and (b) SEM image of the top-gated graphene FET using the  $Al_2O_3$  nanosheet (Inset: higher magnification of 50 nm  $Al_2O_3$  nanosheet on graphene). (c) Output curve and (d) transfer curve of fabricated top-gated graphene FET.

nated from the imbalanced carrier injection caused by misalignment between the contact electrode work function and channel neutrality points.<sup>31</sup> Also this asymmetry may come from the residues of PAA on the graphene channel or adsorbent properties of graphene from the open area of channel near the edge of source and drain electrodes where the NS is not attached. These values are larger or similar to other top-gated graphene FETs using plasma-assisted ALD  $Al_2O_3$  directly on graphene (720 cm<sup>2</sup>/(V s))<sup>10</sup> and transferred gate stacks on graphene (800–2000 cm<sup>2</sup>/(V s)).<sup>17</sup> And the top-gated graphene FET shows good performance with very low leakage currents of ~1.0 × 10<sup>-9</sup> A and ~4.1 × 10<sup>-10</sup> A at  $V_G = -5$  and 5 V, respectively. Also we did the device stability test and it shows quite stable performance over 1000 times of measurement (see Figure S4 in the Supporting Information).

## CONCLUSION

A new strategy is demonstrated to integrate graphene with high-quality, physically transferrable  $Al_2O_3$  NS. The  $Al_2O_3$  NS functions as a dielectric layer with a dielectric constant of 9 and zero hysteresis. Additionally,  $Al_2O_3$  NS shows enhanced dielectric properties such as a lower  $D_{it}$  value and a smaller flat band voltage shift than Th-ALD  $Al_2O_3$  thin film. Using the  $Al_2O_3$  NS as a gate dielectric, top-gated monolayer graphene FETs are fabricated with excellent performance and high mobilities of 2200 cm<sup>2</sup>/(V s) and 800 cm<sup>2</sup>/(V s) for the hole and electron, respectively, which are better than previously

reported values. This is a feasible method through which highperformance graphene devices can be fabricated without any chemical or physical treatment on graphene. With further optimization of the NS transfer process and assembly technique, large arrays of top-gated graphene FETs or other physically-assembled electronic devices can be manufactured. Thus, this physically transferrable NS fabrication method can provide a broad, practical approach for high-performance graphene devices and various flexible electronic devices.

# ASSOCIATED CONTENT

#### **S** Supporting Information

Further experimental information and stability of devices. This material is available free of charge via the Internet at http:// pubs.acs.org/.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: hyungjun@yonsei.ac.kr. Tel : +82-2-2123-5773. Fax: +82-2-313-2879.

#### **Author Contributions**

<sup>II</sup>Authors H.J. and J.P. contributed equally.

### Notes

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

This research was supported by the Converging Research Center Program through the Ministry of Education, Science and Technology (2013K000173) and by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (NRF-2010-0024066). Also this work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST) (2011-0028594) and by the Industrial Strategic technology development program (10041926, Development of high density plasma technologies for thin film deposition of nanoscale semiconductor and flexible display processing) funded by the Ministry of Knowledge Economy.

## REFERENCES

(1) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. *Science* **2004**, *306*, 666–669.

(2) Bolotin, K. I.; Sikes, K. J.; Jiang, Z.; Klima, M.; Fudenberg, G.; Hone, J.; Kim, P.; Stormer, H. L. *Solid State Commun.* **2008**, *146*, 351–355.

(3) Lee, Y.; Bae, S.; Jang, H.; Jang, S.; Zhu, S.-E.; Sim, S. H.; Song, Y. I.; Hong, B. H.; Ahn, J.-H. *Nano Lett.* **2010**, *10*, 490–493.

(4) Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Ri Kim, H.; Song, Y. I.; Kim, Y.-J.; Kim, K. S.; Ozyilmaz, B.; Ahn, J.-H.; Hong, B. H.; Iijima, S. *Nat. Nanotechnol.* **2010**, *5*, 574–578.

(5) Dimiev, A.; Kosynkin, D. V.; Sinitskii, A.; Slesarev, A.; Sun, Z.; Tour, J. M. *Science* **2011**, *331*, 1168–1172.

(6) Wang, X.; Tabakman, S. M.; Dai, H. J. Am. Chem. Soc. 2008, 130, 8152–8153.

(7) Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Nat. Nanotechnol. 2008, 3, 654–659.

(8) Zou, K.; Hong, X.; Keefer, D.; Zhu, J. Phys. Rev. Lett. 2010, 105, 126601.

(9) Moon, J. S.; Curtis, D.; Hu, M.; Wong, D.; McGuire, C.; Campbell, P. M.; Jernigan, G.; Tedesco, J. L.; VanMil, B.; Myers-Ward,

- R.; Eddy, C.; Gaskill, D. K. *IEEE Electron Device Lett.* 2009, 30, 650-652.

- (10) Nayfeh, O. M.; Marr, T.; Dubey, M. *IEEE Electron Device Lett.* **2011**, *32*, 473–475.

- (11) Williams, J. R.; DiCarlo, L.; Marcus, C. M. Science 2007, 317, 638–641.

- (12) Lee, B.; Park, S.-Y.; Kim, H.-C.; Cho, K.; Vogel, E. M.; Kim, M. J.; Wallace, R. M.; Kim, J. *Appl. Phys. Lett.* **2008**, *92*, 203102–3.

- (13) Farmer, D. B.; Gordon, R. G. Nano Lett. 2006, 6, 699-703.

- (14) Banerjee, S.; Hemraj-Benny, T.; Wong, S. S. Adv. Mater. 2005, 17, 17–29.

- (15) Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. *Appl. Phys. Lett.* **2009**, *94*, 062107–3.

- (16) Liao, L.; Bai, J.; Qu, Y.; Lin, Y.; Li, Y.; Huang, Y.; Duan, X. Proc. Natl. Acad. Sci. U.S.A. 2010, 107, 6711-6715.

(17) Cheng, R.; Bai, J.; Liao, L.; Zhou, H.; Chen, Y.; Liu, L.; Lin, Y.-C.; Jiang, S.; Huang, Y.; Duan, X. P. Proc. Natl. Acad. Sci. U.S.A. 2012, 109, 11588–11592.

- (18) Chae, S. H.; Yu, W. J.; Bae, J. J.; Duong, D. L.; Perello, D.; Jeong, H. Y.; Ta, Q. H.; Ly, T. H.; Vu, Q. A.; Yun, M.; Duan, X.; Lee, Y. H. Nat. Mater. **2013**, *12*, 403–409.

- (19) Wilson, C. A.; Grubbs, R. K.; George, S. M. Chem. Mater. 2005, 17, 5625-5634.

- (20) Ren, Y.; Zhu, C.; Cai, W.; Li, H.; Hao, Y.; Wu, Y.; Chen, S.; Piner, R. D.; Wu, Q.; Ruoff, R. S. *Nano* **2012**, *07*, 1150001.

- (21) Seguini, G.; Cianci, E.; Wiemer, C.; Saynova, D.; van Roosmalen, J. A. M.; Perego, M. *Appl. Phys. Lett.* **2013**, *102*, 131603–131603-5.

(22) Buckley, J.; De Salvo, B.; Deleruyelle, D.; Gely, M.; Nicotra, G.; Lombardo, S.; Damlencourt, J. F.; Hollinger, P.; Martin, F.; Deleonibus, S. *Microelectron. Eng.* **2005**, *80*, 210–213.

(23) Wang, Y. y.; Ni, Z. h.; Yu, T.; Shen, Z. X.; Wang, H. m.; Wu, Y. h.; Chen, W.; Shen Wee, A. T. *J. Phys. Chem. C* **2008**, *112*, 10637–10640.

(24) Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; Banerjee, S. K.; Colombo, L.; Ruoff, R. S. *Science* **2009**, *324*, 1312–1314.

(25) Dlubak, B.; Kidambi, P. R.; Weatherup, R. S.; Hofmann, S.; Robertson, J. Appl. Phys. Lett. 2012, 100, 173113–173113-4.

(26) Shu-Jen, H.; Zhihong, C.; Bol, A. A.; Sun, Y. IEEE Electron Device Lett. 2011, 32, 812-814.

(27) Bai, J.; Liao, L.; Zhou, H.; Cheng, R.; Liu, L.; Huang, Y.; Duan, X. *Nano Lett.* **2011**, *11*, 2555–2559.

(28) Rodriguez, S.; Vaziri, S.; Ostling, M.; Rusu, A.; Alarcon, E.; Lemme, M. C. *RF ECS Solid State Lett.* **2012**, *1*, Q39–Q41.

(29) Misewich, J. A.; Martel, R.; Avouris, P.; Tsang, J. C.; Heinze, S.; Tersoff, J. *Science* **2003**, *300*, 783–786.

(30) Chen, Y.-F.; Fuhrer, M. S. Phys. Rev. Lett. 2005, 95, 236803.

(31) Farmer, D. B.; Golizadeh-Mojarad, R.; Perebeinos, V.; Lin, Y.-M.; Tulevski, G. S.; Tsang, J. C.; Avouris, P. *Nano Lett.* **2009**, *9*, 388– 392.